# Octagon Sat-PLL-LNB mit 10 MHz-Referenz-Anbindung

Die Firma Octagon fertigt günstige LNBs für Satellitenfernsehempfang, die eine eingebaute PLL-Frequenzaufbereitung haben. Die LO-Frequenz wird intern aus einem 27 MHz-Quarz abgeleitet. Im Gegensatz zu DRO-LNBs weisen die Signale aus diesem LNB eine deutlich bessere Frequenzstabilität und ein geringeres Phasenrauschen auf. Damit sind diese LNBs gut zur Beobachtung des SSB/CW-Bereiches inklusive der Bakenfrequenzen im 10 GHz-Band geeignet. Ein Empfänger auf handlichen 618 MHz kann zum Empfang genutzt werden.

**Problemstellung:** Trotz der schon relativ ordentlichen Frequenzstabilität und -genauigkeit driftet der lokale Oszillator bei Temperaturschwankungen um einige Kilohertz. Es ist wünschenswert, diesen an einen Mutteroszillator anbinden zu können, um diese Drifts zu beseitigen.

## **Aufbau**

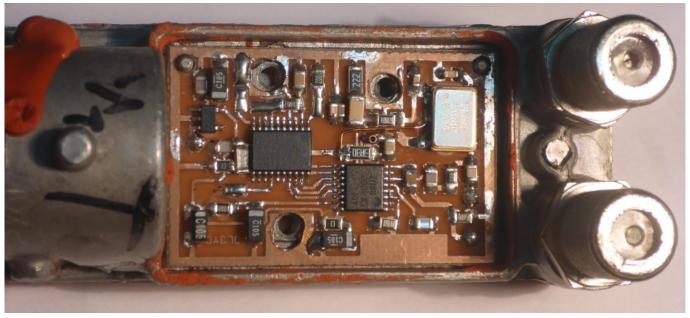

Das Dual-LNB besitzt auf der Oberseite das 10 GHz-Frontend für beide Polarisationen sowie auch einen der beiden Downconverter (inkl. PLL-LO, Mischer und ZF). Auf der Unterseite ist lediglich ein zweiter Downconverter zu finden - zwei F-Buchsen stellen die unabhängigen Downconverter-Ausgänge zur Verfügung.

### **Bild der Oberseite:**

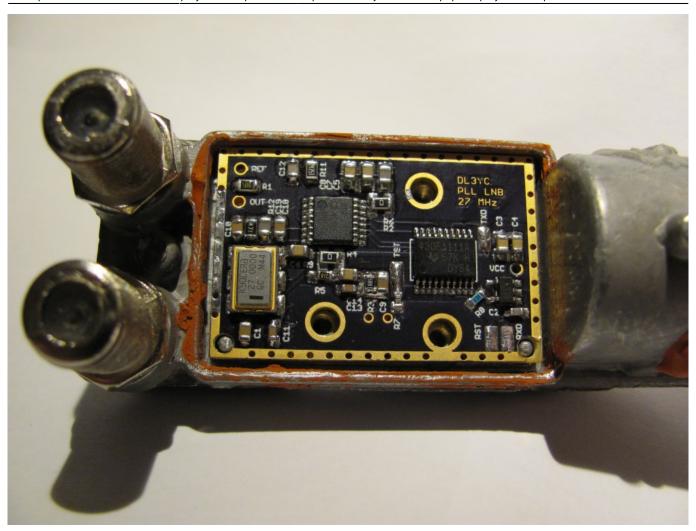

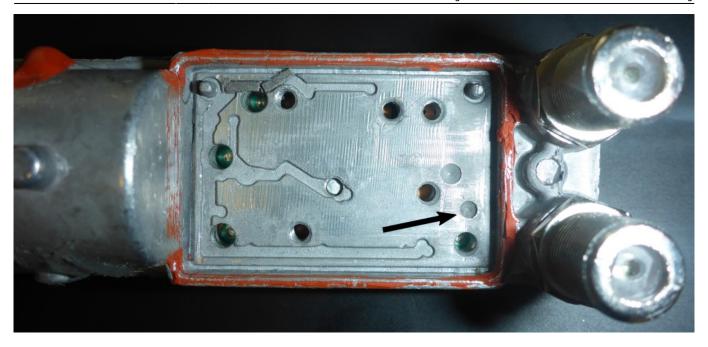

#### **Bild der Unterseite:**

Für Horizontale und Vertikale Polarisation gibt es je ein Frontend bestehend aus einem LNA und einem Verstärker, ein Splitter teilt das verstärkte Signal auf die beiden Downconverter auf. Diese besitzen jeweils einen weiteren Verstärker pro Polarisation, dessen Spannungsversorgungen selektiv aktiviert werden. Ein Combiner wird jeweils verwendet um die beiden Verstärkerausgänge zu addieren, danach erreicht das Signal den RDA3565ES.

Die ausgekoppelten Gleichspannungen beider ZF-Ports werden zur Versorgung der einzelnen Downconverter jeweils auf 6 Volt geregelt und zusätzlich über Dioden zusammengeschaltet um das Frontend zu versorgen. So wird das gemeinsame Frontend versorgt, sobald einer der beiden ZF-Ports Spannung liefert.

Zum zweiten Downconverter existieren folgende Durchkontaktierungen (Positionsangaben beziehen sich auf das Bild des unteren Downconverters):

- GND oben links (nicht lötbar)

- 10 GHz-Input H oben links

- 10 GHz-Input V unten links

- Vcc (5,3V) mittig links

- ZF-Ausgang unten rechts

- GND oben rechts (nicht lötbar)

## **Umsetzung**

Die untere Leiterplatte wird entfernt und gegen die PLL-Leiterplatte ausgetauscht. Über den zweiten - dadurch unnötigen - ZF-Ausgang kann die 10 MHz-Referenz zugeführt werden. Die obere Leiterplatte wird inklusive dem darauf befindlichen Downconverter weiterverwendet. Einzige Änderung hier ist die Entfernung des 27 MHz-Quarzes und die Einspeisung des 27 MHz-Taktes von der PLL-Leiterplatte.

Sebastian hat eine mechanisch passende Leiterplatte entwickelt, deren Design-Files hier herunterzuladen sind:

#### • Version 2:

Schaltplan: Eagle, PDF

Layout: Eagle

Digikey-Warenkorb:

BOM

Sofware:

ZIP

### • Version 1:

• Schaltplan: Eagle, PDF

Layout: EagleSofware: ZIP

In Version 2 wurden die Befestigungslöcher korrigiert und die Bauteile so angeordnet, dass der Originaldeckel verwendet werden kann.

Hier Bilder der aufgebauten Hardware (Version 1 und Version 2) anstelle des zweiten Downconverters:

Der auf der Leiterplatte befindliche MSP430 programmiert die ADF4002-PLL und rastet damit den 27 MHz-VCXO auf die angelegte 10 MHz-Referenz. Nach erfolgreicher Inbetriebnahme ist eine Abstimmspannung von etwa 1,7 Volt am VCXO zu messen.

Um die 27 MHz vom VCXO auf die obere Leiterplatte zu führen kann ein bereits vorgebohrtes Loch einfach ausgebohrt werden. Es empfiehlt sich, hierfür einen 3,2mm-Bohrer zu benutzen. Die obere Leiterplatte wird durchbohrt, man landet in einem Stück Massefläche in der Region des Quarzes, das nicht weiter benötigt wird. Eine der beim Ausbau gewonnenen Durchkontaktiernieten kann wiederverwendet werden und führt das 27 MHz-Signal nach oben, wo es mit einem kleinen Stück Draht an das naheliegendste Pad des ehemaligen Quarzes geführt wird. Das aufzubohrende Loch ist in der unten stehenden Grafik mit einem Pfeil markiert.

http://loetlabor-jena.de/ Printed on 2025/11/25 18:47

From:

http://loetlabor-jena.de/ - Lötlabor Jena

Permanent link:

http://loetlabor-jena.de/doku.php?id=projekte:3cmpllInb:start&rev=1532258794

Last update: 2018/07/22 11:26