2025/11/25 18:52 1/3 Codename Dvorak

## **Codename Dvorak**

Wie weit kann man gehen?

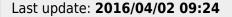

Es soll ein Software Defined Radio(SDR) entstehen, das mit unseren Möglichkeiten einen möglichst hohen Frequenzbereich als Direct Sampler empfangen kann. Somit ist es ein **Mikrowellen-SDR**. Der angepeilte Frequenzbereich ist das 23cm-Amateurfunkband. Dies umfasst **1240 - 1300 MHz**. Als Aufbau gilt wieder der Aufbau als Direct Sampler mit Digital Down Converter im FPGA und Basisbanddemodulation im PC:

## **Analog/Digital-Wandler**

Es wurde die Produktpalette von Linear Technology, Analog Devices, Maxim Semiconductor und Texas Instruments untersucht. Die Wahl fiel auf einen ADC08500 von National Semiconductor(heute Texas Instruments), der eine Analogbandbreite von 1700MHz besitzt.

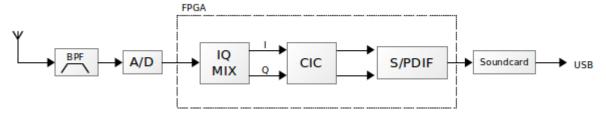

Die maximale Samplerate findet sich auch im Namen wieder: 500Msps. Somit ist es möglich das 23cm-Band in der 5. bzw. 6. Nyquist-Ebene zu empfangen.

Optimal ist eine Samplerate von 340Msps. Dadurch liegt die Mitte der 8. Nyquist-Ebene in der Bandmitte und es sind rund 60Mhz Abstand zwischen den Bandgrenzen und der nächst niedrigeren bzw. höheren Nyquist-Ebene. Der Empfangsbereich erstreckt sich dann von 1190 - 1360 MHz. Dies ist interessant für die Dimensionierung des Bandpasses vor dem ADC. Da Signale unter 1140MHz in das Nutzband gespiegelt werden, muss der Bandpass dort hinreichend stark dämpen. Analog auch für Signale über 1420MHz.

Die Leistung eines ADC definiert sich wesentlich durch den verwendeten Wandler-Takt. Das Jittern des Takts macht sich als erhöhtes Empfängerrauschen bemerkbar. Es sei auf folgendes Dokument verwiesen: Clock jitter analyzed in the time domain von Texas Instruments

### **Testsystem**

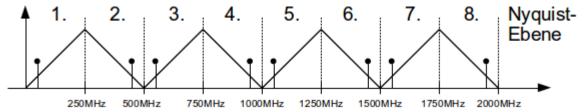

Es wurde ein maximal simpler Testaufbau realisiert. Als Grundlage dient das DE0-Nano FPGA-Entwicklungsboard von Terasic mit einem Cyclone IV. Der ADC ist auf einer Aufsteckplatine platziert:

Rechts sind die Koax-Buchsen für den Antennenanschluss und den Takteingang zu sehen. Eine 3er Pinleiste ist für S/PDIF vorgesehen.

Eine Vielzahl an Bauelementen sind recyclet: Spannungsregler(LM1117) und Baluns für 23cm und Takt sind von einer Radiosonde RS92.

Messung des Eingangs-Baluns, der auf der Wettersonde für GPS(1,6GHz) benutz wurde:

Als Taktgenerator wird ein Si570 in bekannter Ausführung nach DG8SAQ verwendet. Die Frequenz des ADC-Takts wird per CFGR(Windows) oder usbsoftrock(Linux) am PC eingestellt. Sie muss aktuell bei 4096\*48kHz=196,608MHz liegen.

Der Takt wird im ADC durch 2 geteilt und pro Takt 2x8Bit angeboten. Im aktuellen Aufbau werden aber nur 8Bit benutzt. Somit entsteht eine effektive Samplerate von 98,304MHz.

Die Schnittstelle zum PC wird wieder mit einer Soundkarte per S/PDIF mit 48kHz Samplerate realisert. Dadurch werden direkt die I/Q-Signale zum PC zur Demodulation übermittelt. Zur Veränderung der LO-Frequenz dient eine USB-Seriell-Schnittstelle.

#### Messungen

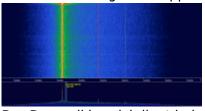

Vollaussteuerung bei knapp 1296MHz mit +10dBm:

Der Dynamikbereich liegt bei ca. 110dB, das Spektrum bei Ansteuerung mit -95dBm:

Aus den Messungen ergibt sich eine relativ schlechte Spiegelfrequenzunterdrückung von 85dB. Die Ursache gilt es noch zu finden.

Am Rauschen ist der Frequenzgang des CIC-Dezimators zu erkennen. Das gilt es noch zu kompensieren.

http://loetlabor-jena.de/ Printed on 2025/11/25 18:52

2025/11/25 18:52 3/3 Codename Dvorak

# Schnittstelle zum SDR-Programm

Die Schnittstelle zwischen Hardware und üblichen SDR-Programmen wie PowerSDR, SDR#, Winrad, usw. ist **ExtIO**. Die Spezifikation ist bei Winrad zu finden.

Als Grundlage wird das ExtIODLL example verwendet. To be continued...

From:

http://loetlabor-jena.de/ - Lötlabor Jena

Permanent link:

http://loetlabor-jena.de/doku.php?id=projekte:dvorak:start&rev=1459589075